Đồng tổng hợp kiến trúc lưới thao tác cho lõi CPU RISC

TÓM TẮT

Bài báo trình bày phương pháp đồng tổng hợp kiến trúc khối tính toán và xử lý trên lưới thao tác

của lõi CPU RISC cho các hệ xử lý chức năng bằng cách tổ hợp hóa cấu trúc ô lưới thao tác, sử

dụng lưới phụ và tái cấu hình lưới bằng phần mềm không những giúp tiết kiệm tài nguyên phần

cứng mà vẫn bảo đảm chức năng xử lý cơ sử dữ liệu có kích thước khác nhau.

Bạn đang xem tài liệu "Đồng tổng hợp kiến trúc lưới thao tác cho lõi CPU RISC", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Đồng tổng hợp kiến trúc lưới thao tác cho lõi CPU RISC

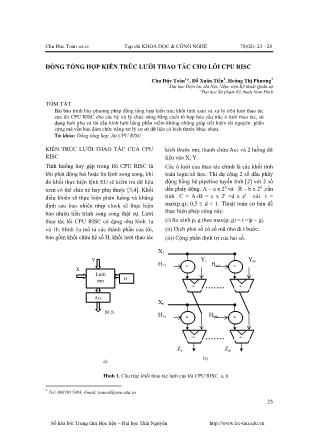

Chu Đức Toàn và cs Tạp chí KHOA HỌC & CÔNG NGHỆ 78(02): 23 - 28 23 ĐỒNG TỔNG HỢP KIẾN TRÖC LƢỚI THAO TÁC CHO LÕI CPU RISC Chu Đức Toàn1*, Đỗ Xuân Tiến2, Hoàng Thị Phƣơng3 1Đại học Điện lực Hà Nội, 2Học viện Kỹ thuật Quân sự 3Đại học Sư phạm Kỹ thuật Nam Định TÓM TẮT Bài báo trình bày phƣơng pháp đồng tổng hợp kiến trúc khối tính toán và xử lý trên lƣới thao tác của lõi CPU RISC cho các hệ xử lý chức năng bằng cách tổ hợp hóa cấu trúc ô lƣới thao tác, sử dụng lƣới phụ và tái cấu hình lƣới bằng phần mềm không những giúp tiết kiệm tài nguyên phần cứng mà vẫn bảo đảm chức năng xử lý cơ sử dữ liệu có kích thƣớc khác nhau. Từ khóa: Đồng tổng hợp, lõi CPU RISC KIẾN TRÚC LƢỚI THAO TÁC CỦA CPU RISC Tình huống hay gặp trong lõi CPU RISC là khi phát động hai hoặc ba lệnh song song, khi đó khối thực hiện lệnh EU sẽ kiểm tra dữ liệu xem có thể chia xẻ hay phụ thuộc [3,4]. Khối điều khiển sẽ thực hiện phân luồng và khẳng định sau bao nhiêu nhịp clock sẽ thực hiện bao nhiêu tiến trình song song thật sự. Lƣới thao tác lõi CPU RISC có dạng nhƣ hình 1a và 1b. Hình 1a mô tả các thành phần của lõi, bao gồm khối chứa hệ số H, khối lƣới thao tác kích thƣớc mn, thanh chứa Acc và 2 luồng dữ liệu vào X, Y. Các ô lƣới của thao tác chính là các khối tính toán logic/số học. Thí dụ cộng 2 số dấu phẩy động bằng hệ pipeline tuyến tính [2] với 2 số dấu phẩy động: A = a x 2p và B = b x 2q ,cần tính C = A+B = c x 2 r =d x z s với r = max(p,q); 0,5 d < 1. Thuật toán cơ bản để thực hiện phép cộng này: (i) So sánh p, g theo max(p, g) = t =|p g|. (ii) Dịch phải số có số mũ nhỏ đi t bƣớc. (iii) Cộng phần định trị của hai số. * * Tel: 0982917093; Email: [email protected] Hmn + + * * Y1 Ym X1 H11 * * Xn H1n Z1 Zm + + Hm1 b) H Y BUS Acc X Lƣới mn a) Hình 1. Cấu trúc khối thao tác lƣới của lõi CPU RISC a, b. Số hóa bởi Trung tâm Học liệu – Đại học Thái Nguyên Chu Đức Toàn và cs Tạp chí KHOA HỌC & CÔNG NGHỆ 78(02): 23 - 28 24 Hình 2. Tính cộng 2 số dấu phẩy động trên hệ pipeline tuyến tính Nhận xét: Cấu trúc pipeline hình 2 có 4 tầng (số tầng sẽ khác nhau cho các cấu trúc tính khác nhau), tức là sau 4 chu kỳ clock khối này mới hoạt động thực sự song song. Nếu chỉ một lần tính thì không có vấn đề về điều khiển, nhƣng nếu phải tính cho một chuỗi dữ liệu thì vấn đề điều khiển sẽ phức tạp do phải đồng bộ các thành phần tham gia vào quá trình xử lý nhƣ bộ điều khiển luồng, bộ đếm độ giữ chậm của các khâu, bộ điều khiển quay vòng...Nhiều khi độ phức tạp quá mức của cơ cấu điều khiển có thể dẫn tới những nguy hiểm tiềm tàng: mất đồng bộ, trễ do phải chờ tập kết đủ yếu tố. Trong các hệ xử lý chức năng, khi nhiệm vụ là cụ thể và hạn chế trong một lớp bài toán nào đấy thì việc loại trừ ảnh hƣởng trên có nhiều giải pháp. Một trong những giải pháp đó là chúng ta có thể tổ chức phần cứng của lƣới thao tác bằng hệ tổ hợp thuần túy. Căn cứ vào [1,5] các cấu trúc các chức năng cơ bản của hệ tổ hợp là rõ ràng nhƣ bộ cộng, trừ nhị phân, BCD có dấu. Còn các cơ cấu nhân chia ta sẽ sử dụng phép dịch phải (chia 2), dịch trái (nhân 2), phần dƣ và phần carry sẽ sử dụng một cấu trúc riêng. Một cấu trúc điển hình của phép nhân/chia bằng hệ tổ hợp đƣợc thể hiện trên hình 3. Hình 3. Cấu trúc bộ nhân/chia của ô lƣới thao tác bằng cấu trúc NOT, AND, OR và MUX trõ |p-q| TG dÞch ph¶i TG dÞch Bé ®Õm B = b x 2q A = a x 2 p L0 L1 L2 L3 L4 d S C = d . 2s = A+B chän ®Þnh trÞ t ®Þnh trÞ + sè mò I1 O1 Số nhân/chia dn d0 MUX Im O2 m BUS BUS MUX Dn I1 Im O1 O2 m MUX D1 I1 Im O1 O2 m MUX I1 Im O1 O2 m Số hóa bởi Trung tâm Học liệu – Đại học Thái Nguyên Chu Đức Toàn và cs Tạp chí KHOA HỌC & CÔNG NGHỆ 78(02): 23 - 28 25 Thừa số thứ nhất Dn-D1 đƣa vào đầu data của MUX, thừa số thứ hai các bit điều khiển ghép kênh. Khi đó ta có bảng 1. Với cách dich trên, phép nhân chỉ nhân thừa số thứ hai với các số 2n, với n=1,2,3Khi cần nhân với số bất kỳ, ta chỉ cần kết hợp một số cấu trúc trên để có kết quả đúng. Thực chất chỉ cần sử dụng 2 tầng hệ tổ hợp là ta có kết quả với mọi giá trị thừa số trong phép lấy tích (thƣơng). Nhƣ vậy trên nguyên lý tập đủ [5], kết hợp với các công nghệ đƣơng đại nhƣ công nghệ PLA, FPGA có thể tổng hợp đƣợc một lƣới thao tác với các phép tính cần thiết mà không gặp trở ngại lớn nào. Điều quan trọng là những cấu trúc đó chỉ cần một nhịp clock là chúng đã thực hiện xong thao tác của mình (về lý thuyết nhịp clock có thể có tần số bất kỳ). ĐỒNG TỔNG HỢP LƢỚI THAO TÁC CHO CPU RISC Bây giờ ta xét sâu vào phân tích hoạt động của lõi CPU RISC cho trƣờng hợp dữ liệu vectơ, khi luồng dữ liệu đi vào lƣới thao tác với tốc độ lớn do chỉ cẩn quản lý thứ tự phần tử. Khi đó nếu luồng X và luồng Y đủ số lƣợng n, m phần tử và các hệ số H đã điền đầy lƣới thì cần 1 nhịp clock sẽ cho kết quả Z. Với Z đƣợc tính bằng: n j Zi 1 XiHijYi ; (i= m,1 ; j= n,1 ) Tuy nhiên khi dung lƣợng dữ liệu cần xử lý lớn hơn khả năng xử lý một lần của cấu trúc này thì cần phải tổ chức lƣới thao tác phức tạp hơn thì mới bảo đảm hiệu năng cao. Lƣới thao tác đƣợc tổ chức nhƣ hình 4b. Bộ đệm lƣới có cấu trúc giống nhau và có đƣờng dẫn pipeline tƣơng ứng cho từng ô lƣới. Chỉ cần một nhịp clock (có thể nhịp clock này lớn hơn nhịp clock hệ thống) là copy toàn bộ nội dung bộ đệm lƣới sang lƣới thao tác. Bảng 1. Phép nhân với các số 2n Thừa số thứ nhất 1 2 4 8 16 Thừa số thứ hai Im-I1 0..00 0..01 0..10 0..11 0..100 Bƣớc dịch trái 0 1 2 3 4 Tích =thừa số thứ nhất =2 lần thừa số thứ nhất =4 lần thừa số thứ nhất =8 lần thừa số thứ nhất =16 lần thừa số thứ nhất Bảng 2. Phép nhân với các số bất kỳ Thừa số thứ nhất 1 2 3 4 5 6 7 8 Tích Cấu trúc nhân1 Cấu trúc nhân2 Cấu trúc nhân2 + Cấu trúc nhân1 Cấu trúc nhân4 Cấu trúc nhân4 + Cấu trúc nhân1 Cấu trúc nhân4 + Cấu trúc nhân2 Cấu trúc nhân4 + Cấu trúc nhân2 + Cấu trúc nhân1 Cấu trúc nhân8 Hình 4. Cấu trúc khối thao tác lƣới của lõi CPU RISC khi kích thƣớc ô nhớ trong FIFO x (m,n) hfifo Acc fifo Lƣới mn X Y BUS b) Copy trong 1 nhịp clock a) Lƣới nm Bộ đệm B ộ đ ệm lƣ ớ i Số hóa bởi Trung tâm Học liệu – Đại học Thái Nguyên Chu Đức Toàn và cs Tạp chí KHOA HỌC & CÔNG NGHỆ 78(02): 23 - 28 26 Cấu trúc này bảm đảm là hệ số H đƣợc nạp vào ô lƣới trƣớc khi dữ liệu cần xử lý tới ô lƣới. Bộ đệm chứa hệ số H và Acc có cơ cấu FIFO giúp tăng dung lƣợng xử lý. Nếu kích thƣớc ô nhớ trong FIFO x (m,n) và dung lƣợng dữ liệu cần xử lý bằng x*X thì chỉ cần= x+1 chu kỳ nhịp clock sẽ hoàn tất thao tác. Trƣờng hợp dữ liệu khác nhau về kích thƣớc (kích thƣớc phần tử có thể là 8 bit, 16 bit, 32 bit...) thì thay vì sử dụng nhiều lƣới thao tác, có thể tổng hợp một cấu trúc kết hợp cả khâu tổ chức phần cứng và khâu xây dựng lệnh nhằm tái cấu hình lƣới thao tác theo kích thƣớc dữ liệu. Làm đƣợc điều này giúp giảm thiểu tài nguyên phần cứng của hệ thống đi rất nhiều. Cơ cấu điều khiển chia lƣới theo phƣơng án này bao gồm thanh ghi điều khiển chia lƣới thành m cột n hàng và đƣợc dùng nhƣ một lệnh mà khối EU của CPU thực hiện nhƣ những lệnh khác. Điều này giúp mềm hóa cấu hình của lƣới thao tác. Số lƣợng cột sẽ nằm trong khoảng 1 Mm max còn số lƣợng hàng trong khoảng 1 Nn max . Đây chính là phhƣơng pháp tổng hợp cả phần cứng và cả phần mềm trên cùng trên một bƣớc : Phần cứng là tổ chức lƣới thao tác trên công nghệ FPGA, nơi mỗi ô lƣới là một hệ tổ hợp phức tạp gồm các cấu trúc tính toán cùng các mạch phụ trợ NOT AND OR và MUX sao cho đầu vào là tập hợp bit địa chỉ có số lƣợng là k (2 k Mmax ) cho chia cột và có số lƣợng q (2q Nmax )cho chia hàng. Cú pháp của lệnh chia cột và hàng có thể thiết kế nhƣ: lệnh MOV Colreg, DivX hoặc MOV Rowreg, DivX với X=1 đến maxM (maxN) sẽ thực hiện gán số chia lƣới thành các phần. Lập tức các thanh ghi điều khiển sẽ ánh xạ vào phần cứng của lƣới để tái tổ chức lại cấu hình lƣới thao tác theo yêu cầu. Nếu maxM=maxN=64 bit thì lệnh chia cột (hàng) đƣợc thể hiện trên bảng 3. Nếu dung lƣợng dữ liệu cần xử lý vƣợt dung lƣợng các bộ đệm FIFO thì cần cơ cấu lặp để vẫn sử dụng thuật toán cũ. Khi đó cần cơ cấu điều khiển vòng lặp. Bằng cách này ta có thuật toán lặp mà phần thực hiện chính lại bằng phần cứng nên tốc độ sẽ vƣợt trội so với thuật toán lặp thuần túy bằng phần mềm (hình 5). Bảng 3. Phân chia lƣới thao tác Số chia Div1 Div2 Div3 Div4 Div5 ------- Div64 Số lƣợng bit/ô lƣới thao tác (bit/ô) 64 32 21 16 12 ------ 1 Số dƣ (bit) 0 0 1 0 2 ------ 0 Hình 5. Cấu trúc khối thao tác lƣới của lõi CPU RISC khi kích thƣớc ô nhớ trong fifo x (m,n) B ộ đ ệm l ƣ ớ i Y BUS X hfifo Acc fifo B ộ đ iề u k h iể n d ịc h v ò n g Lƣới mn Số hóa bởi Trung tâm Học liệu – Đại học Thái Nguyên Chu Đức Toàn và cs Tạp chí KHOA HỌC & CÔNG NGHỆ 78(02): 23 - 28 27 Toàn bộ cấu trúc đƣợc tổng hợp nhƣ trên cho phép phát động các tiến trình song song ngay trong lõi CPU RISC bằng 1 dòng lệnh. Nếu đƣa dòng lệnh dạng: repeat 16 hfifo = [r0++], fth, hth vào cấu trúc phần cứng đƣợc tổ chức nhƣ trên ta có vế trái repeat 16 hfifo = [r0++] là tiến trình lặp 16 vòng, mỗi vòng là một lần tải data từ bộ nhớ hệ thống vào bộ đệm hfifo còn vế phải là 2 tiến trình: (i) fth là tiến trình copy hệ số từ hfifo vào ô lƣới thao tác phụ; (ii) hth là tiến trình copy hệ số từ ô lƣới thao tác phụ vào ô lƣới thao tác chính. Phân tích quá trình thực hiện lệnh trên bằng đồ thị thời gian dễ dàng nhận thấy chúng là 3 tiến trình song song do các bƣớc thực hiện đƣợc xếp chồng về mặt thời gian (hình 6). Nhƣ vậy, trừ 2 nhịp clock đầu tiên là t0 và t1 thì từ t2 trở đi 3 tiến trình hfifo = [r0++]; fth; hth là thực hiện song song thật sự giúp tăng tốc độ tính toán đáng kể (trƣờng hợp cực đại sẽ là 3 lần). KẾT LUẬN Nếu cấu trúc ô lƣới thao tác đƣợc tổ chức dƣới dạng hệ tổ hợp thì thời gian thực hiện tính toán toàn bộ n hàng của lƣới chỉ tiêu tốn đúng 1 chu kỳ clock. Nếu sử dụng công nghệ FPGA thì tính khả thi của thiết kế ô lƣới thao tác, nhất là đối với hệ chức năng, khi mà các phép tính là hạn chế trong một lớp bài toán cụ thể. Đồng tổng hợp giúp bổ xung vào tập lệnh những lệnh mới nhằm đạt hiệu năng cao nhất mà không phá vỡ kiến trúc Harvart của CPU RISC. TÀI LIỆU THAM KHẢO [1]. Lê Xuân Bằng.Kỹ thuật số.Nxb Khoa học kỹ thuật, 2009, Tr131-148. [2]. Đỗ Xuân Tiến. Kỹ thuật vi xử lý và lập trình Assembly cho hệ vi xử lý. Nxb Khoa học kỹ thuật, 2009. [3]. Kai Hwang, Faye A.Briggs. Computer architecture and parallel processing. McGraw- Hill Book Company [4]. Richard Cloutier, Synthesis of Pipelined Instruction Set Processors, Ph.D. dissertation, Dept. of Electrical and Computer Engineering, Carnegie Mellon University, 1993. Alsoavailable as a Research Report No. CMUCAD-93-03. [5]. Raymond E.Miller.Swiching theory. John Wiley & Sons, Inc. Hình 6. Hoạt động của lƣới thao tác gồm 3 tiến trình song song (hệ số H có giá trị từ h11 đến hnm) H1 H2 H3 H4 H1 H2 H3 H1 H2 H5 H4 H3 hfifo ô lƣới phụ ô lƣới chính t0 t1 t2 t3 t4 pipeline pipeline pipeline pipeline Nhịp clock Số hóa bởi Trung tâm Học liệu – Đại học Thái Nguyên Chu Đức Toàn và cs Tạp chí KHOA HỌC & CÔNG NGHỆ 78(02): 23 - 28 28 SUMMARY CO-SYNTHESIZE A ARCHITECTURE OF THE OPRATION GRID FOR CPU RISC CORE Chu Duc Toan1*, Do Xuan Tien2, Hoang Thi Phuong3 1Electric Power University, 2Academy of Technology and Military,, 3Nam Dinh University of Technology Education This paper presents a co-synthesis method of the architecture of culculating and processing block on operation grid of CPU RISC core for functional microprocessor systems by combinational circuits. Using a slave grid and reconfiguration master grid by software, not only helps to economize hardware resources but still guarantees the functional processability for database with diffrent sizes. Key words: Co-synthesize a architecture, CPU RISC core * Tel: 0982917093; Email: [email protected] Số hóa bởi Trung tâm Học liệu – Đại học Thái Nguyên

File đính kèm:

dong_tong_hop_kien_truc_luoi_thao_tac_cho_loi_cpu_risc.pdf

dong_tong_hop_kien_truc_luoi_thao_tac_cho_loi_cpu_risc.pdf